FPGA教程系列:Vivado中CIC与FIR IP核深度解析

CIC滤波器原理概述

Cascaded Integrator-Comb(简称CIC)滤波器,也被称为Hogenauer滤波器,是一种广泛应用于数字信号处理领域的多速率滤波结构。它特别适用于采样率远高于信号实际带宽的系统场景,例如在数字上变频器(DUC)和数字下变频器(DDC)中的应用。

该滤波器的最大优势在于其硬件实现仅依赖于加法器、减法器和延迟单元,无需使用乘法器,因此在FPGA等资源受限平台上具有极高的实现效率,是进行大幅采样率变换的理想选择。

IP核参数配置详解

滤波器类型设置(Filter Specification)

Filter Type(滤波模式)

- Interpolation(插值):用于提升输出采样率。例如,将1kHz输入信号通过4倍插值后变为4kHz输出。

- Decimation(抽取):用于降低输出采样率。例如,将4kHz输入信号经4倍抽取后得到1kHz输出。

Number Of Stages(级联阶数)

此参数决定CIC滤波器的积分与梳状部分的级数。增加阶数可增强阻带衰减能力,有效抑制杂散频率成分,但同时会增大通带内的幅度波动,并提高资源消耗。通常推荐取值范围为2至5,属于关键性能权衡项。

Differential Delay(差分延迟M值)

该参数影响梳状滤波器的响应特性:

- M=1:通带响应最平坦,适合对通带纹波敏感的应用,但阻带衰减较慢。

- M=2:阻带衰减速度比M=1快约6dB,但通带纹波更大。

Number Of Channels(通道数量)

支持并行处理多路独立数据流。若需同时处理如立体声音频的左右声道,可将其设为大于1的值。

采样率变化配置(Sample Rate Change Specification)

Sample Rate 模式选择

- Fixed(固定模式):插值或抽取倍率在IP生成时即确定,运行期间不可更改。

- Programmable(可编程模式):允许在系统运行过程中通过外部端口动态调整倍率,提供更高的灵活性。

Fixed Or Initial Rate(初始倍率R值)

设定固定的采样率变换比例。在插值模式下,输出频率 = 输入频率 × R;在抽取模式下,输出频率 = 输入频率 ÷ R。

Minimum Rate / Maximum Rate(最小/最大倍率)

仅当选择Programmable模式时生效,用于定义运行时可调节的倍率范围。

Sample RateProgrammable硬件时序配置(Hardware Oversampling Specification)

Rate Specification(速率指定方式)

- Frequency Specification:通过直接输入数据采样频率和系统时钟频率来建立时序关系。

- Period Specification:通过指定每个样本所占的时钟周期数来进行配置。

Input Sample Frequency (MHz)

设置输入数据流的原始采样频率。

Clock Frequency (MHz)

定义IP核工作所需的主时钟频率。为了保证足够的计算时间,系统时钟必须显著高于输入或输出采样率。

Sample Period (Clock Cycles)

表示每个输入样本对应的时钟周期数目。该值由工具根据以下两项自动计算得出,确保数据采样与处理同步准确:

Clock FrequencyInput Sample Frequency

数值精度配置(Numerical Precision)

Input Data Width(输入位宽)

设置输入数据的二进制位数。位宽越大,表示的动态范围越广,精度越高,但也意味着更多逻辑资源的占用,尤其影响乘法相关模块。

Output Data Width(输出位宽)

通常由工具基于输入位宽、滤波器阶数及增益特性自动推导。用户也可手动修改,但应确保不低于理论所需最小值,以避免溢出或精度损失。

Quantization(量化方式)

- Full Precision(全精度):在整个计算流程中保留原始浮点系数精度,仅在最终输出阶段执行一次量化,精度最高,资源开销最大。

- Truncate(截断):在中间运算过程中直接舍去低位数据,节省资源但可能引入较大误差。

Filter Options可选功能配置(Optional Features)

Use DSP48 Slice(启用DSP48资源)

决定是否利用FPGA内部专用的DSP48硬核进行乘法运算。

- 勾选:乘法操作由高性能DSP48模块完成,速度快、资源占用少,强烈建议启用。

- 不勾选:乘法由通用逻辑单元(LUT+FF)实现,极大消耗逻辑资源且性能较低。

Use Streaming Interface(启用流式接口)

启用后,IP核将采用AXI4-Stream协议进行数据传输,适用于高速连续数据流场景。

TVALIDTREADYTLASTFIR滤波器

AMD LogiCORE? IP FIR 编译器内核提供了一种高度可参数化、面积优化且高性能的通用接口,用于实现灵活的FIR滤波器设计。该IP核支持多种配置选项,便于在不同应用场景中构建高效的信号处理流水线。

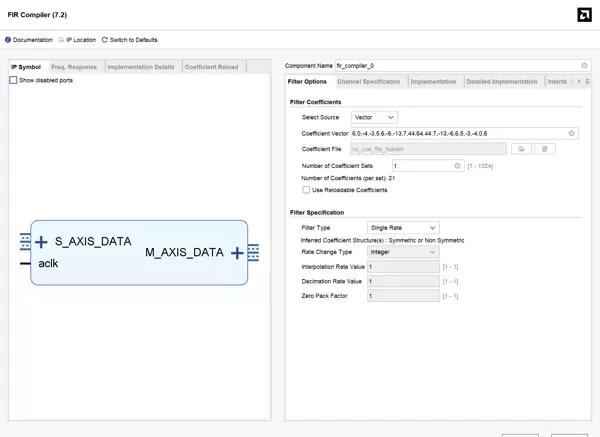

滤波器规格(Filter Specification)

Filter Type(滤波器类型)

- Single Rate(单速率):输入与输出采样率相同,适用于常规滤波任务。

- Interpolation(插值):提升输出采样率,实现上采样功能。

- Decimation(抽取):降低输出采样率,常用于下采样处理。

此外,还支持希尔伯特变换(Hilbert)模式,适用于特定信号处理需求。

Inferred Coefficient Structure(推断系数结构)

- Symmetric(对称):利用系数对称性,节省约50%的乘法器资源。

- Anti-Symmetric(反对称):适用于某些特殊类型的滤波器设计。

- Non-Symmetric(非对称):无结构限制,资源消耗最大。

Rate Change Type(速率变化类型)

- Integer(整数倍):插值或抽取因子为整数,实现简单高效。

- Fractional(分数倍):支持非整数倍采样率变换,灵活性更高但复杂度增加。

Interpolation Rate Value(插值因子):输出采样率 = 输入采样率 × 插值因子。

Decimation Rate Value(抽取因子):输出采样率 = 输入采样率 ÷ 抽取因子。

Zero Pack Factor(零填充因子):用于控制数据打包方式,影响数据流的组织形式。

Filter Coefficients(滤波器系数)

Select Source(选择来源):IP核支持两种系数输入方式:

- Vector(向量):直接在配置界面输入系数值,适合简单滤波器设计。

- File(文件):通过外部COE文件导入系数,适用于复杂或需复用的设计场景。

Coefficient Vector(系数向量):决定滤波器的频率响应特性。

Number of Coefficients(每组系数数量):即滤波器阶数,直接影响性能和硬件资源占用。

Number of Coefficient Sets(系数组数量):表示支持的滤波通道数量,适用于多通道并行处理,如多载波通信系统中的应用。

Use Reloadable Coefficients(可重载系数)

- 未勾选:系数固定不可变,适用于静态滤波需求。

- 勾选:允许在运行时动态更新系数,适用于自适应滤波等动态场景。

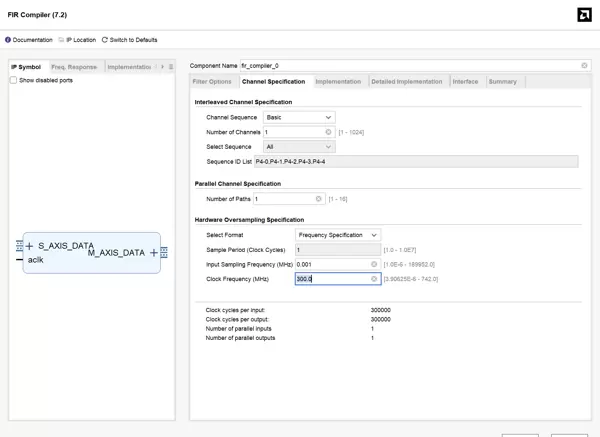

Interleaved Channel Specification(交织通道规格)

Channel Sequence(通道序列)

- Basic:基本模式,适用于单通道或少量通道的简单应用。

- Advanced:高级模式,支持复杂的通道顺序和映射配置。

Number of Channels(通道数量):定义需要同时处理的独立数据通道总数。

Select Sequence(选择序列):

- All:处理所有启用的通道。

- Custom:用户自定义处理哪些通道。

Sequence ID List(序列ID列表):用于设定各通道的处理顺序及其标识信息。

Parallel Channel Specification(并行通道规格)

Number of Paths(路径数量):指定并行处理的数据路径数量,提升吞吐能力。

Hardware Oversampling Specification(硬件过采样规格)

Select Format(选择格式):

- Frequency Specification:以频率参数直接定义过采样行为。

- Sample Period:通过设置时钟周期数来控制采样间隔。

Control Options(控制选项)

ACLKEN:是否启用时钟使能信号。

- 若勾选,则IP核将增加一个

? 输入端口。当该信号为高电平时,IP正常工作;为低电平时,暂停操作,有助于降低功耗并实现系统级同步。ACLKEN

ARESETn:是否启用异步复位信号。

- 若勾选,则引入一个低电平有效的

? 输入端口。当此信号有效时,IP内部所有寄存器立即复位至初始状态,是系统初始化和错误恢复的关键机制。ARESETN

Output TREADY:决定输出端口是否包含

TREADY- 勾选:输出接口采用完整的AXI4-Stream握手协议(

?/TVALID

?),支持背压机制。当下游模块无法及时接收数据时,可通过拉低TREADY

? 通知FIR核暂停发送,从而避免数据丢失。TREADY - 不勾选:输出接口不含

信号,FIR核持续输出数据,适用于不会发生拥塞的简单系统结构。TREADY

该IP核可与DMA或其他IP(如FFT、CIC)无缝级联,采用无地址的连续数据流协议,非常适合构建高效的数据处理流水线。

Sample Period (Clock Cycles)(采样周期):每个采样点所占用的时钟周期数量。

Clock Frequency (MHz)(时钟频率):FPGA 内部运行的工作时钟频率。

Input Sampling Frequency (MHz)(输入采样频率):对输入信号进行采样的频率值。

Coefficient Type(系数类型):用于设定系数值的符号属性,决定是否支持负数。

Quantization(量化方式):确定系数在系统中的存储格式。

- Integer Coefficients:以整数形式保存系数,实现结构简单,资源消耗低。

- Fractional Coefficients:以小数形式表示系数,可提供更高的数值精度。

Coefficient Width(系数位宽):影响滤波器的精度以及 FPGA 资源的使用量,位宽越大,精度越高,资源占用也越多。

Best Precision Fraction Length(最佳精度小数长度):系统自动优化系数的小数部分位数,以达到最优精度表现。

Coefficient Fractional Bits(系数小数位):手动指定系数中小数部分所占的位数。

Coefficient Structure(系数结构):定义滤波器系数的对称性,影响乘法器资源的使用效率。

- 对称系数:利用系数对称特性,可节省约 50% 的乘法器资源。

- 反对称系数:适用于某些特定类型的滤波器设计。

- 非对称系数:无结构优化,资源消耗最大。

Input Data Type(输入数据类型):设置输入数据的符号属性。

- Signed:支持正负信号,常用于音频、传感器等双极性数据处理。

- Unsigned:仅处理非负数值,适用于图像等单极性信号场景。

Input Data Width(输入数据位宽):决定输入信号的动态范围和分辨率。

Input Data Fractional Bits(输入数据小数位):定义输入数据中用于表示小数部分的位数。

Output Rounding Mode(输出舍入模式):控制最终输出结果的舍入策略。

- Full Precision:保留全部计算过程中的精度,防止误差累积。

- Truncation:直接截断多余位数,实现简单但可能引入舍入误差。

- Round to Nearest:采用四舍五入方式,兼顾精度与实现复杂度。

Output Width(输出位宽):决定输出数据的精度和表示范围。其最大值可通过以下公式估算:

输入位宽 + 系数位宽 + log(系数数量) = 最大输出位宽。

Output Fractional Bits(输出小数位):设定输出数据中小数部分所占的位数。

TLAST(最后一个数据包指示):启用或禁用 TLAST 信号,用于标识当前数据流是否为最后一个数据包。

Output TREADY(输出就绪信号):控制是否使用 TREADY 信号实现背压机制,调节数据流传输节奏。

Input FIFO(输入FIFO缓冲):在输入端口添加 FIFO 缓冲区,提升数据吞吐稳定性。

TUSER(用户自定义字段选项):

- Input TUSER:决定输入数据流中是否包含用户自定义信息。

- Output TUSER:决定输出数据流中是否携带用户自定义字段。

- User Field Width:设定用户自定义字段的位宽大小。

Synchronization Mode(同步模式):配置数据写入时的同步机制。

- On Vector:按向量单位同步,适合批量加载配置参数。

- On Element:按元素逐个同步,适用于细粒度配置更新。

Configuration Method(配置方法):定义配置数据的传输路径。

- Single:使用单一通道完成配置,结构简洁。

- Multiple:支持多通道并行配置,提高配置效率。

Reload Channel Options(重载通道选项):设定系统可同时保存的滤波器系数组数量,便于快速切换。

ARESETn(异步复位,低电平有效):提供异步复位功能,要求有效电平持续至少两个时钟周期以确保可靠复位。

ACLKEN(时钟使能):启用时钟门控,可在不需要运算时关闭时钟以降低功耗。

Reset Data Vector(复位数据向量):在复位期间将输出数据向量恢复至预设初始值。

Blank Output(空白输出):复位过程中将输出置于高阻态或无效状态,避免误信号输出。

其余未提及的选项可保持默认设置,通常已满足大多数应用场景需求。

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号