| 架构核心 | 发布年份 | 代表特性 | 典型芯片平台 |

| Cortex-M0 | 2009 | 超低功耗、ARMv6-M 内核 | STM32F0, NXP LPC800 |

| Cortex-M0+ | 2012 | 优化功耗与指令执行路径 | STM32G0, Kinetis L |

| Cortex-M3 | 2006 | 基于 ARMv7-M,性能提升明显 | STM32F1, EFM32 |

| Cortex-M4 | 2010 | DSP 指令 + 单精度 FPU 支持 | STM32F3/F4, Kinetis K |

| Cortex-M7 | 2014 | 双发射流水线,高性能 | STM32F7, H7 系列 |

| Cortex-M23/M33 | 2016+ | TrustZone 安全扩展,ARMv8-M 架构 | 多家 ARMv8-M 芯片 |

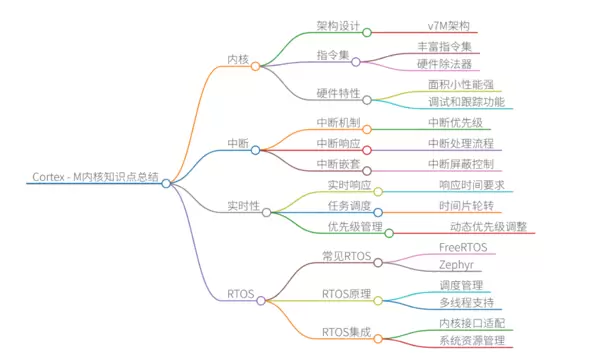

一、Cortex-M 系列家族划分

Cortex-M 系列处理器根据性能、指令集支持和功能特性划分为多个子系列,适用于不同复杂度和功耗要求的应用场景。

Cortex-M 核心设计特点:

- 简化开发模型:采用线性地址空间、统一的 NVIC 中断控制器,无需 MMU 支持,便于嵌入式系统开发。

- 高效中断响应:中断延迟可控制在 12 个时钟周期以内,适合实时控制任务。

- Thumb 指令集支持:提供高代码密度,有效节省 Flash 存储空间。

- 多种低功耗模式:支持 SLEEP、DEEPSLEEP、STOP 和 STANDBY 等模式,满足节能需求。

典型应用场景推荐:

| 应用场景 | 推荐核心 | 原因说明 |

| 简单 IO 控制 / 极低功耗场景 | M0+ | 指令集精简,运行功耗极低,适合小型传感器节点或基础控制逻辑 |

| 普通 RTOS 实时系统应用 | M3 | 完整支持 Thumb-2 指令集,性能均衡,生态系统成熟稳定 |

| 电机驱动、音频信号处理 | M4 | 具备 DSP 指令和可选单精度 FPU,结合 CMSIS-DSP 库效率更高 |

| 实时音视频传输、图形界面渲染 | M7 | 高频主频配合 Cache 和双发射流水线,数据吞吐能力强 |

Cortex-M 系列性能对比表:

| 特性 | Cortex-M0 | Cortex-M3 | Cortex-M4 | Cortex-M7 |

| 指令宽度 | Thumb 16-bit | Thumb-2 | Thumb-2 + DSP | Thumb-2 + DSP + FPU |

| 流水线深度 | 3-stage | 3-stage | 3-stage | 6-stage dual-issue |

| FPU 支持 | 无 | 无 | 可选单精度 | 单精度/双精度 |

| DSP 扩展 | 无 | 无 | 有 | 有(更强性能) |

| 最大主频 | ~48 MHz | ~100 MHz | ~180 MHz | ~480 MHz(如 STM32H7 系列) |

| NVIC 可配置中断数 | 32 个 | 240 个 | 240 个 | 240 个 |

补充说明:

指令宽度与执行效率:

Cortex-M0 仅支持 16 位 Thumb 指令,结构简单,适合资源受限环境;M3 及以上版本全面支持 Thumb-2 混合指令集(16/32 位),提升编码灵活性和运行效率。M4 和 M7 进一步引入 DSP 指令集,其中 M7 更支持单精度甚至双精度浮点运算单元(FPU),显著增强数字信号处理能力。

流水线深度与吞吐性能:

更深的流水线有助于实现更高的主频和并发处理能力。M7 采用六级双发射(dual-issue)流水线架构,能够在同一周期内执行两条指令,大幅提升整体运算吞吐量。

NVIC 中断管理能力:

M0 最多支持 32 个外部中断源,适用于外设较少的轻量级应用;而 M3/M4/M7 均支持最多 240 个可屏蔽中断,更适合需要连接大量外设或运行复杂操作系统的场合。

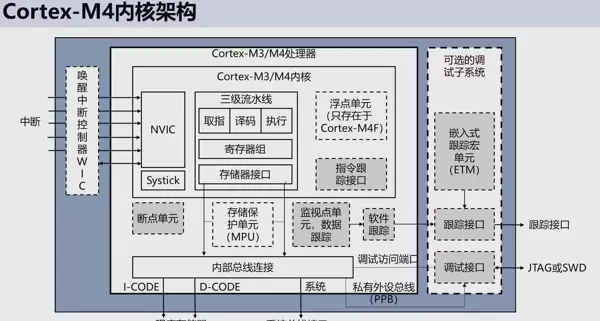

二、内核寄存器与特殊功能模块

Cortex-M 架构除了标准通用寄存器之外,还包含多个关键系统级寄存器和专用外设模块,用于控制处理器行为和响应事件。

主要通用与系统寄存器:

| 寄存器 | 描述 | 说明 |

| R0~R12 | 通用数据寄存器 | 用于传递函数参数、存储返回值及临时变量 |

| SP | 栈指针(Stack Pointer) | 可切换为主栈 MSP 或进程栈 PSP |

| LR | 链接寄存器(Link Register) | 保存 BL 指令跳转前的返回地址 |

| PC | 程序计数器(Program Counter) | 指向当前正在执行的指令地址 |

| xPSR | 程序状态寄存器 | 整合 APSR(应用状态)、IPSR(中断状态)、EPSR(执行状态)以及 IT 条件和 GE 字段 |

SysTick 定时器功能详解:

该定时器常用于操作系统节拍调度或精确延时控制。

| 寄存器 | 功能说明 |

| CTRL | 控制位:启动定时器、使能中断、查看状态 |

| LOAD | 设置重装载值,决定定时周期 |

| VAL | 当前倒计数值,读取时自动清除计数标志 |

| CALIB | 提供校准信息,确保每毫秒精度准确 |

SysTick->LOAD = SystemCoreClock / 1000 - 1;

SysTick->VAL = 0;

SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk |

SysTick_CTRL_TICKINT_Msk |

SysTick_CTRL_ENABLE_Msk;NVIC(嵌套向量中断控制器)

NVIC 是 Cortex-M 中断管理的核心组件,其寄存器映射起始于地址 0xE000E100。

关键寄存器包括:

:用于启用或禁用特定中断NVIC_ISER / NVIC_ICER

:配置每个中断的优先级(高位优先)NVIC_IPRx

:软件触发中断请求,调试和测试常用NVIC_STIR

NVIC_SetPriority(USART1_IRQn, 5); // 优先级越小越高

NVIC_EnableIRQ(USART1_IRQn);中断优先级机制解析:

- 抢占优先级(Preemption Priority):决定一个中断是否可以打断另一个正在执行的中断服务例程。

- 子优先级(Sub Priority):当多个中断具有相同抢占优先级时,决定它们的响应顺序。

SCB->AIRCR = (0x5FA << 16) | (3 << 8); // PRIGROUP = 3中断嵌套与屏蔽机制:

NVIC 允许高优先级中断打断低优先级中断,实现中断嵌套。可通过以下方式控制中断屏蔽:

- 使用

和__disable_irq()

寄存器进行精细控制__enable_irq() - 通过 PRIMASK 或 BASEPRI 寄存器实现全局或分级中断屏蔽

__disable_irq(); // 全局中断屏蔽(设置 PRIMASK)

__enable_irq(); // 恢复中断软件触发中断示例:

NVIC->STIR = EXTI0_IRQn; // 触发 EXTI0 中断中断服务函数编写示例:

void USART1_IRQHandler(void) {

if (USART1->SR & USART_SR_RXNE) {

char c = USART1->DR; // 读取接收数据

// 后续处理逻辑

}

}工程实践建议:

- 中断服务程序应尽量简短,避免长时间占用 CPU

- 禁止在中断中调用 malloc、new 等动态内存分配函数

- 避免阻塞操作或耗时计算,必要时通过标志位交由主循环处理

- 合理规划中断优先级分组策略,防止优先级反转或响应延迟

三、启动流程概述

当 Cortex-M 处理器上电或复位后,首先从“复位向量”开始执行初始化流程。

| 地址偏移 | 内容 | 说明 |

| 0x00 | 初始栈顶指针(MSP 初始值) | 指示主栈的起始位置 |

| 0x04 | 复位向量(Reset Vector) | 指向复位处理函数(如 Reset_Handler) |

后续向量表依次存放 NMI、HardFault、SVCall 等异常入口地址,构成完整的中断向量表结构。

复位后,Cortex-M 系列处理器默认使用主堆栈指针(MSP)作为初始堆栈。此时,栈顶指针 SP 被初始化为指向主栈区域的起始地址,通常由启动代码完成这一配置。

Reset_Handler:

LDR R0, =_estack

MOV SP, R0 ; 初始化堆栈

BL SystemInit ; 系统时钟初始化

BL __libc_init_array ; C 库初始化

BL main ; 跳转主函数在典型的 STM32 启动流程中,启动代码以汇编语言编写,负责系统运行前的关键初始化操作:

- 设置堆栈指针(SP)

- 初始化

.data段和.bss段 - 调用 SystemInit 函数进行系统时钟等底层配置

- 跳转至 C 语言入口函数(如 main 函数)

.bss.dataSystemInit()main()Thumb 指令集与执行效率优化

Cortex-M 架构仅支持 Thumb 和 Thumb-2 指令集,不兼容传统的 ARM 32-bit 指令模式。这种设计有助于提升指令预取效率并减少总线带宽占用。

Thumb 模式:采用 16 位压缩指令格式,有效节省 Flash 存储空间,适用于简单操作场景。

Thumb-2 技术:融合 16 位与 32 位指令,兼顾代码高密度与复杂运算能力,在保持紧凑性的同时支持更丰富的功能。

// 16 位 Thumb-2 指令

MOVS R0, #1 ; 小指令快速赋值

// 32 位 Thumb-2 指令

BL 0x08001234 ; 远距离函数调用异常与中断机制分类

| 异常类型 | 编号 | 描述 |

|---|---|---|

| Reset | -3 | 上电或软件触发的系统复位 |

| NMI | -2 | 不可屏蔽中断,优先级极高 |

| HardFault | -1 | 所有未被处理的异常最终汇聚于此 |

| MemManage/BusFault/UsageFault | -12 ~ -10 | 可选的系统级故障异常 |

| SVC | -5 | 系统服务调用,常用于 RTOS 中的特权模式切换 |

| PendSV | -2 | 可挂起的调用中断,用于上下文切换 |

| SysTick | -1 | 系统节拍定时器中断 |

| 外部中断(EXTI) | 0 ~ n | 对应具体外设,如 GPIO、USART、DMA 等 |

异常处理的基本流程如下:

- 处理器自动将当前上下文压入堆栈

- 根据向量表跳转至对应的中断服务例程(ISR)

- 执行 ISR 处理逻辑

- 通过异常返回机制恢复现场

- 程序返回到原任务继续执行

异常返回过程依赖于 EXC_RETURN 值,该值存储在 LR(链接寄存器)中,用于指示:

- 返回时使用的堆栈指针(MSP 或 PSP)

- FPU 单元是否需要恢复

- 目标运行模式(Thread Mode 或 Handler Mode)

- 是否进行特权等级切换

BX LR__asm("BX LR");实时响应能力分析

实时性是嵌入式控制系统的核心指标之一,决定了设备能否在限定时间内对外部事件做出及时响应。得益于低延迟中断机制与精简指令集架构,Cortex-M 微控制器广泛应用于各类实时控制场合。

1. 实时性分类

硬实时(Hard Real-Time):必须严格满足时间约束,超时可能导致严重后果,典型应用包括电机驱动、飞行姿态控制等。

软实时(Soft Real-Time):允许偶发延迟,但整体响应需维持在可接受范围内,常见于数据采集、音频流处理等场景。

2. 任务调度策略

抢占式调度:高优先级任务可中断正在运行的低优先级任务,确保关键操作获得即时响应。

时间片轮转(Round-Robin):相同优先级的任务按时间片轮流执行,保障系统调度公平性。

优先级管理机制:

- 静态优先级:任务优先级在系统设计阶段固定设定。

- 动态优先级:根据任务状态或资源等待情况动态调整,可用于解决优先级反转等问题。

3. Cortex-M 对实时性的硬件支持

- NVIC 支持中断嵌套与抢占,实现极低延迟响应(通常小于 12 个 CPU 周期)

- SysTick 定时器提供精确周期中断,适用于裸机环境下的时间片管理或轻量级 RTOS 调度

- 多种低功耗模式(Sleep/Stop/Standby)可结合中断唤醒机制,在节能的同时维持必要的实时响应能力

RTOS 在 Cortex-M 上的应用

实时操作系统(RTOS)是嵌入式领域实现多任务并发与高效调度的重要软件组件。结合 Cortex-M 架构的特性,RTOS 可显著增强系统的任务管理能力和响应性能。

1. RTOS 核心原理

调度管理:RTOS 内核依据任务优先级与运行状态决定下一个执行的任务实体。

多线程支持:每个任务拥有独立的堆栈空间和上下文环境,实现逻辑上的并行执行。

同步与通信机制:提供信号量、互斥锁、消息队列等机制,协调资源访问,避免竞争条件。

2. 主流 RTOS 平台对比

| 名称 | 特点 |

|---|---|

| FreeRTOS | 体积小、移植性强、生态完善,广泛用于 STM32、NXP 等 Cortex-M 设备 |

| Zephyr | 支持多平台,集成网络协议栈与设备模型,适合物联网终端开发 |

| RTX (Keil) | 遵循 CMSIS-RTOS 接口标准,官方深度集成,便于与 ARM 工具链协同工作 |

3. RTOS 与 Cortex-M 的集成方式

内核接口适配:通过 CMSIS-RTOS API 实现对 NVIC 中断控制器和 SysTick 定时器的封装,支撑任务切换与时间管理功能。

系统资源管理:RTOS 统一管理堆栈分配、CPU 使用率监控、中断屏蔽状态,确保各任务间隔离且系统稳定运行。

任务调度优化:

- 支持基于优先级的抢占调度与同优先级的时间片轮转

- 允许配置为抢占或非抢占模式,灵活应对不同实时性需求场景

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号