1. 问题背景

在FPGA设计过程中,经常会遇到管脚连接错误或信号顺序接反的情况。此外,某些应用场景下需要使用FPGA的快速加载模式,而该模式对引脚位置有严格要求。然而,在实际硬件设计中,PCB往往已经定型,若因引脚问题重新改版,不仅耗时且成本较高。面对此类困境,如何在不修改硬件的前提下有效解决问题,成为设计中的关键环节。

2. 解决方案详解

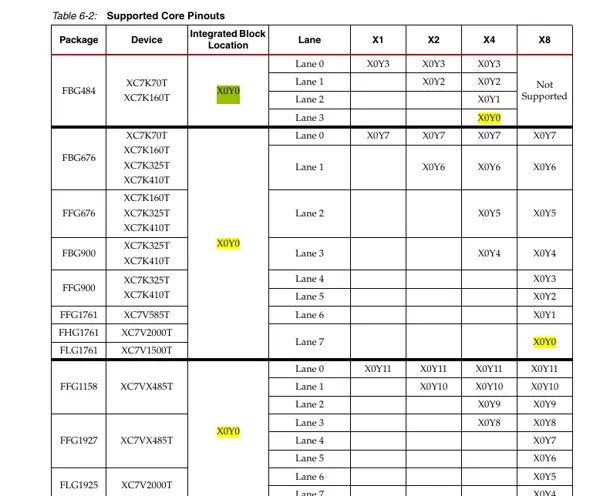

本案例以Xilinx Kintex-7系列FPGA为例进行说明。由于PCIe在FPGA中属于硬核模块,其对应的物理引脚在芯片手册中有明确规定,通常不允许随意更改。但在实际PCB布线过程中,出于走线便利性考虑,可能调整了PCIe差分对的排列顺序,导致上电后系统无法正常识别PCIe设备。

针对此问题,首先应明确:在常规设计中,必须严格按照官方手册推荐的引脚分配进行约束,避免自行定义引发兼容性问题。查阅K7系列GTX相关文档可知,PCIe通道的管脚与FPGA内部逻辑呈现倒序对应关系。

若确实存在物理连接与标准定义不一致的情况,仍可通过软件层面进行修正。具体方法是在XDC约束文件中添加如下配置(以K7-676封装为例,其他型号可参照类似方式调整):

set_property PACKAGE_PIN {} [get_ports RX0_P]

set_property PACKAGE_PIN {} [get_ports RX1_P]

set_property PACKAGE_PIN {} [get_ports RX2_P]

set_property PACKAGE_PIN {} [get_ports RX3_P]

set_property PACKAGE_PIN Y2 [get_ports RX0_P]

set_property PACKAGE_PIN W4 [get_ports RX1_P]

set_property PACKAGE_PIN V2 [get_ports RX2_P]

set_property PACKAGE_PIN U4 [get_ports RX3_P]

上述操作采用先空置再赋值的方式完成引脚重映射,从而实现物理连接与逻辑定义的匹配。由此可见,FPGA平台具备较强的灵活性和容错能力,能够在一定程度上弥补前期硬件设计的不足。

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号