PCIe硬件设计要点解析

PCIe核心概念详解

Lane - 通道

Lane是PCIe中最基本的传输单元,每个Lane由四根信号线构成:

- 两根用于发送数据(TX+ 和 TX-)

- 两根用于接收数据(RX+ 和 RX-)

这种差分信号结构支持全双工通信,允许设备同时进行数据的发送与接收。

Link - 链路

PCIe链路由一个或多个Lane组成。常见的规格如x1、x4、x8、x16表示链路中所包含的Lane数量:

- x1:1个Lane

- x4:4个Lanes

- x16:16个Lanes(常见于显卡插槽)

版本演进与带宽对比

| 版本 | 推出年份 | 单Lane速率 (GT/s) | x1链路带宽 | x16链路带宽 |

|---|---|---|---|---|

| PCIe 1.0 | 2003 | 2.5 | 250 MB/s | 4 GB/s |

| PCIe 2.0 | 2007 | 5.0 | 500 MB/s | 8 GB/s |

| PCIe 3.0 | 2010 | 8.0 | ~1 GB/s | ~16 GB/s |

| PCIe 4.0 | 2017 | 16.0 | ~2 GB/s | ~32 GB/s |

| PCIe 5.0 | 2019 | 32.0 | ~4 GB/s | ~64 GB/s |

| PCIe 6.0 | 2022(发布) | 64.0 | ~8 GB/s | ~128 GB/s |

FPGA平台下的PCIe硬件设计注意事项

本文以Xilinx Ultrascale系列中的KCU060开发板为例,深入探讨PCIe在FPGA硬件实现过程中的关键设计问题。实际上,这部分内容属于标准PCIe硬件架构的设计范畴。

XDMA在Xilinx FPGA中作为硬核模块存在,其物理位置在芯片内部是固定的。因此,在系统设计阶段,首要任务就是明确该模块的具体布局位置,以便正确完成PCB走线和引脚分配。

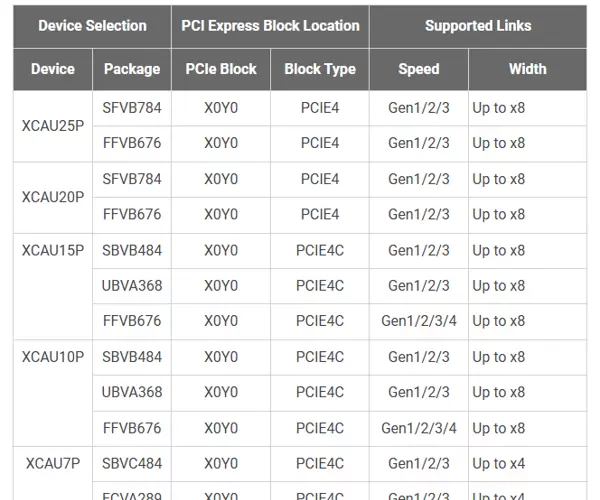

关于FPGA中PCIe资源的位置信息,官方提供了详细的设计参考指南:

图中清晰标注了PCIe硬核所在区域,例如标记为X0Y0的位置。然而,对于初学者而言,可能会困惑于X0Y0究竟对应哪个物理位置,以及各个Lane(如Lane1、Lane2等)对应的管脚是如何分布的。

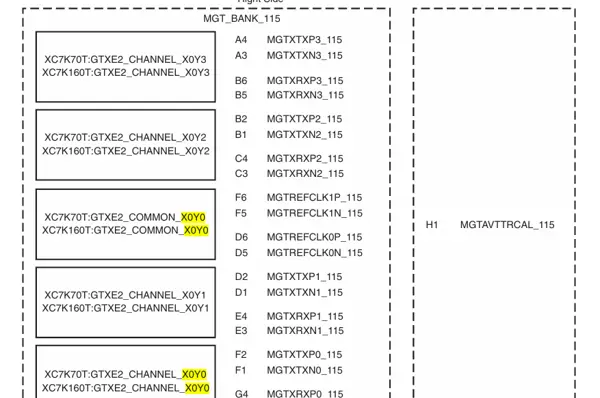

此时需要查阅另一份配套的技术手册来获取更精确的信息:

该文档会列出X0Y0所关联的具体I/O引脚。如图所示,最下方即为X0Y0对应的Lane1管脚位置。但随之而来的问题是:Lane2及其他Lane又位于何处?

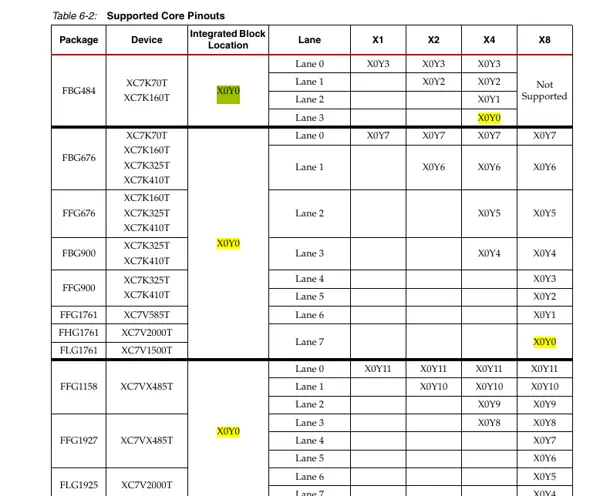

这个问题往往需要进一步查找额外的技术资料才能解答:

这份文档揭示了各Lane的实际映射关系。值得注意的是,其排列顺序具有迷惑性——采用倒序方式呈现。这一特性极易导致新手在设计过程中误接Lane顺序,从而引发PCIe链路无法被识别的硬件故障。

尽管如此,即便出现此类连接错误也并非无解。后续章节将介绍一种无需重新制板即可修复的方法,有效避免因设计失误带来的项目延误和工作压力。

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号