如果应用场景是:

PS 通过 AXI 总线向 FIFO 写入一帧数据 → PL 从 FIFO 读取字节 → 进行串行发送

那么应选择第一项:

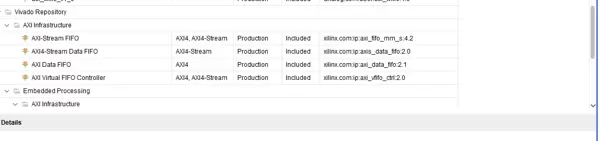

AXI-Stream FIFO

对应的 IP 名称为:

xilinx.com:ip:axi_fifo_mm_s:4.2这个模块也常被称为:

AXI FIFO MM S

之所以推荐该选项,原因如下:

其一端具备 AXI4 / AXI4-Lite memory-mapped 接口,可直接连接至 Zynq MPSoC PS 的 GP 或 HP 端口,使 PS 能够像操作普通外设一样对其进行访问;

另一端则提供 AXI4-Stream 接口,便于后续调制模块使用,输出连续的字节流数据。

tdata/tvalid/tready/tlast这种结构完美匹配“由 PS 写入数据帧、PL 侧按流式消费”的需求,无需用户额外封装 AXI 协议逻辑。

其余几种 FIFO IP 的用途说明(帮助你更好区分):

AXI4-Stream Data FIFO

axis_data_fifo属于纯粹的 AXIS 到 AXIS 流水线缓冲模块,典型用于 DMA→FIFO→IP 这类数据流场景。它不具备供 PS 访问的 memory-mapped 接口,因此不适合需要软件直接写入数据的应用。

AXI Data FIFO

axi_data_fifo实现的是 AXI memory-mapped 到 AXI memory-mapped 的延迟匹配或时序优化功能,主要用于增强总线通道的稳定性与性能,并非设计用来作为“软件可读写的队列”来使用。

AXI Virtual FIFO Controller

axi_vfifo_ctrl用于构建大容量“虚拟 FIFO”,需配合外部存储器(如 DDR)使用,系统结构较复杂。通常应用于视频处理或高速数据通路等场合。对于当前仅 200 bps 的低速应用而言,显然过于冗余,无需采用。

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号