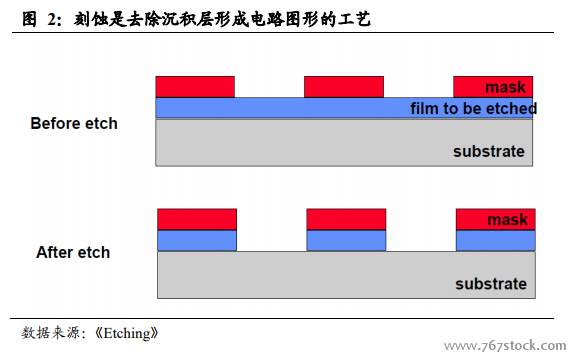

刻蚀是用化学或物理方法对衬底表面或表面覆盖薄膜进行选择性腐蚀或剥离的过程,进而形成光刻定义的电路图形。刻蚀的基本目标是在涂胶的硅片上正确的复制掩模图形。有图形的光刻胶层在刻蚀中不受到腐蚀源显著的侵蚀。这层掩蔽膜用来在刻蚀中保护硅片上的特殊区域而选择性地刻蚀掉未被光刻胶保护的区域。在通常的 CMOS 工艺流程中,刻蚀都是在光刻工艺之后进行的。从这一点来看,刻蚀可以看成在硅片上复制所想要图形的最后主要图形转移工艺步骤。

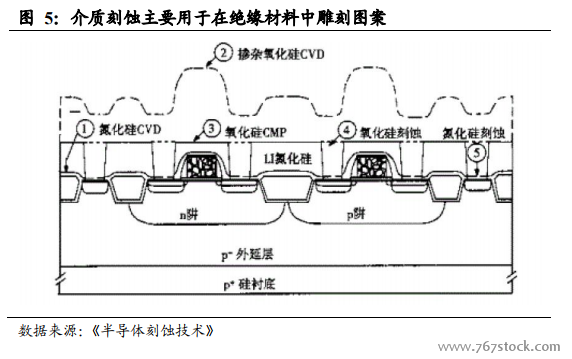

介质刻蚀在绝缘材料中雕刻图案以将半导体器件的导电部分分隔开。 对于先进的设备,这些结构可能具有较高的深宽比,并且涉及复杂、敏感的材料。 与刻蚀参数目标轻微的偏差(即使在原子尺度)也会对器件的质量产生负面影响。介质刻蚀一般要求刻蚀出比较高深宽比的缺口,并且要求下层材料有较高的选择比。

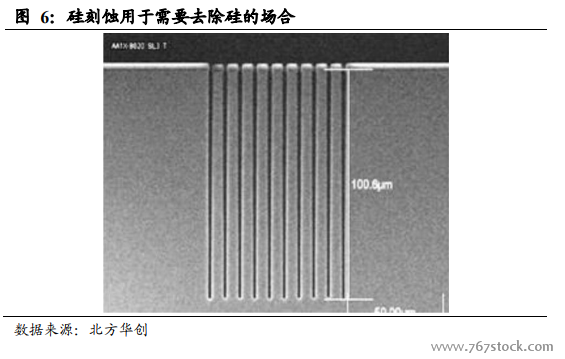

硅刻蚀用于需要去除硅的场合,浅沟槽隔离刻蚀(STI)、多晶硅栅极刻蚀(poly gate)是定义半导体器件尺寸的关键工序。由于技术的不断推进,在传统硅刻蚀的基础上发展出了深硅刻蚀,它有别于 VLSI中的硅刻蚀,因此又称为先进硅刻蚀(ASE) 工艺。它由于采用了感应耦合等离子体(ICP),所以与传统的反应离子刻蚀(RIE)、电子回旋共振(ECR)等刻蚀技术相比,具有更大的各向异性刻蚀速率比和更高的刻蚀速率,且系统结构简单。

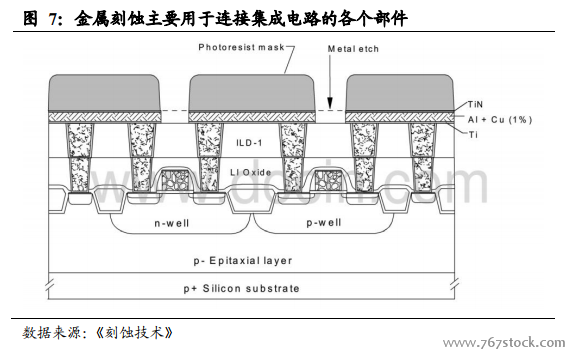

金属蚀刻工艺在连接形成集成电路(IC)的各个部件(例如,形成电线和电连接)中起关键作用。 这些工艺还用于钻穿金属硬掩模(MHM),金属硬掩模用于对传统掩模太小的特征进行图案化,从而允许特征尺寸的持续缩小。金属刻蚀主要步骤分为去除氧化层(自然氧化的铝)、刻蚀其他材料层(如抗反射层)、主刻蚀(铝)、去除残留物的过刻蚀、去除光刻胶。

【备用下载】

半导体刻蚀设备行业深度报告.pdf

(4.34 MB, 需要: 5 个论坛币)

半导体刻蚀设备行业深度报告.pdf

(4.34 MB, 需要: 5 个论坛币)

乐晴智库搜集整理

百度 乐晴智库,更多深度行业研究资料

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号