简介

本文为FPGA学习的第一部分内容,重点讲解其基本逻辑单元的结构与功能。以Xilinx Ultrascale系列FPGA为例,深入解析可编程逻辑块(CLB)的核心组成及其工作原理。

概念介绍

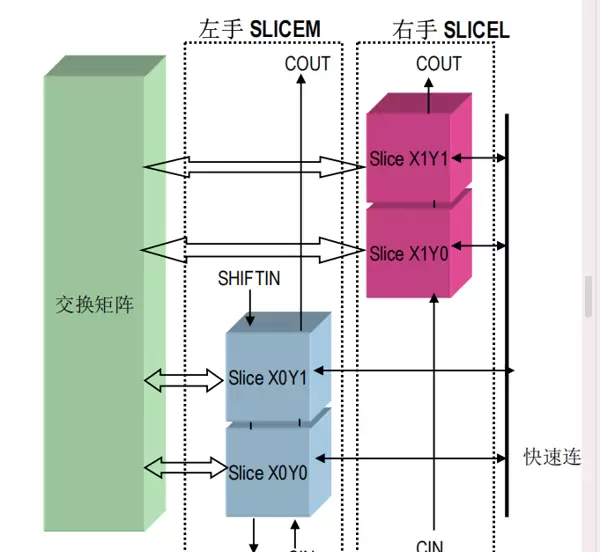

可编程逻辑块是FPGA中实现组合逻辑和时序逻辑的主要资源。在Ultrascale架构中,这些逻辑资源被高度优化,支持高性能与低功耗应用。每个可编程逻辑块通过开关矩阵连接布线资源,具备灵活的数据通路控制能力。

总体结构

Ultrascale架构中的CLB由多个切片(Slice)构成,每个切片包含8个6输入查找表(LUT)和16个触发器。CLB分为高性能和低功耗两种类型,满足不同设计需求。切片是CLB的基本功能单元,主要分为两种类型:SliceL 和 SliceM。

查找表(LUT)

在Ultrascale架构中,切片分为以下两类:

- SliceL:基础逻辑型切片

- SliceM:支持存储功能的增强型切片

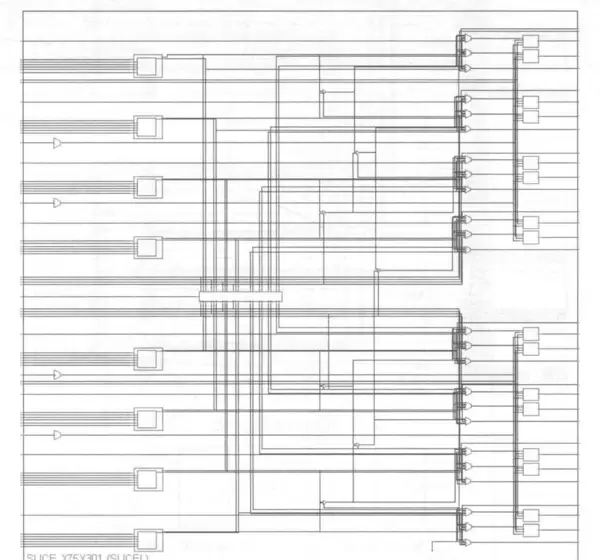

下图为SliceL的内部结构示意图:

该结构包括:

- 8个6输入查找表,标记为A到H(即A、B、C、D、E、F、G、H)

- 右侧集成16个锁存器或触发器资源

- F7、F8、F9类型的多路复用器

- 一个8位进位链模块(CARRY8),位于LUT之后

进位链后配置了F7级多路复用开关,共4个,分别为:

- F7MUXAB

- F7MUXCD

- F7MUXEF

- F7MUXGH

随后是两个F8多路复用器,分别标识为F8MUXTOP(上)和F8MUXBOT(下)。最后是一个F9多路复用器,记作F9MUX,用于更高层级的信号整合。

SLICEM(M代表Memory)除了具备普通LUT功能外,还可将LUT重新配置为以下模式:

- 标准6输入查找表

- 64位分布式RAM

- 32位移位寄存器

此外,单个LUT也可拆分为两个独立的5输入LUT,从而同时实现两组逻辑运算,提升资源利用率。

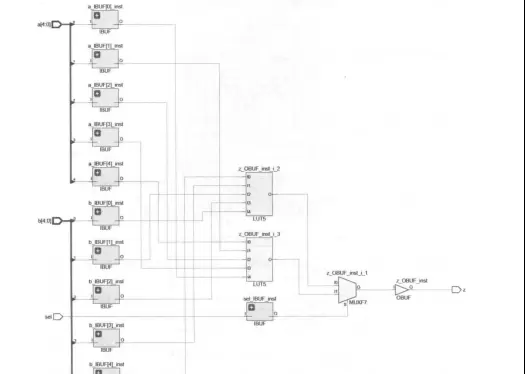

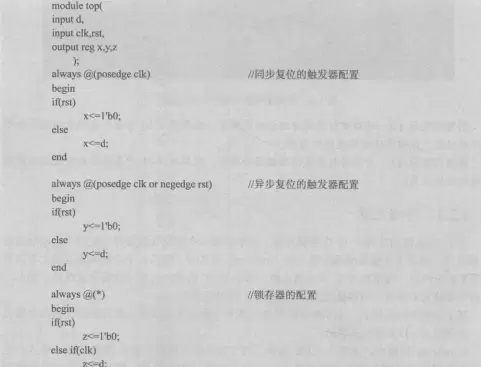

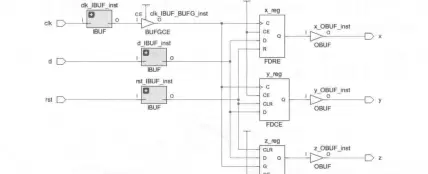

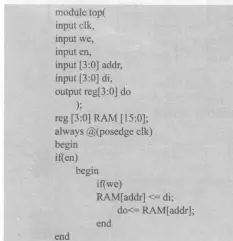

以下是一个简单的Verilog示例,展示多输出逻辑的实现方式:

module top( input [4:0] a, output [5:0] c ); assign c[0] = &a; assign c[1] = ~&a; assign c[2] = &a; assign c[3] = |a; assign c[4] = ^a; assign c[5] = ~^a; endmodule

该代码综合后的FPGA结构如下图所示:

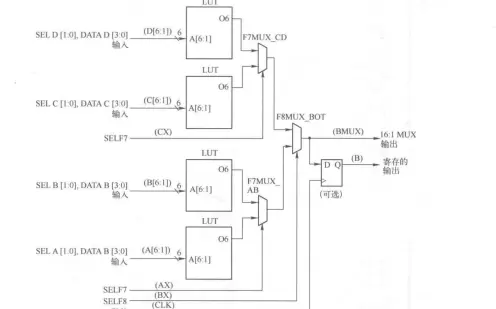

多路复用器

多路复用器在切片中起到关键作用,能够将多个LUT输出合并,实现更宽输入的逻辑函数,最高可达9输入任意函数,甚至部分55输入函数。每个切片配备7个多路复用器,用于构建复杂逻辑结构。

1. F7MUX 类型(F7MUX_AB、F7MUX_CD、F7MUX_EF、F7MUX_GH)

用于合并两个相邻的LUT输出。控制信号来自切片外部的AX、BX、EX、GX。其功能包括:

- 实现7输入逻辑函数

- 构建8:1多路复用器

2. F8MUX 类型(F8MUX_BOT 和 F8MUX_TOP)

用于整合两个F7MUX的输出,控制信号为BX和FX。其用途包括:

- 实现8输入逻辑函数

- 构建16:1多路复用器

3. F9MUX

用于合并两个F8MUX的输出,由外部DX信号控制,可用于:

- 实现辅助的8输入函数

- 实现32:1多路复用器

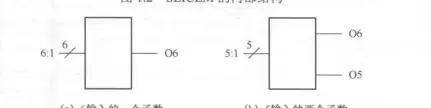

以下为一个多路选择器的设计实例:

module top( input [4:0] a, b, input sel, output z ); wire x, y; assign x = &a; assign y = |b; assign z = sel ? x : y; endmodule

该设计在FPGA中综合后的结果如图所示,可见选择操作由查找表与多路复用器协同完成。

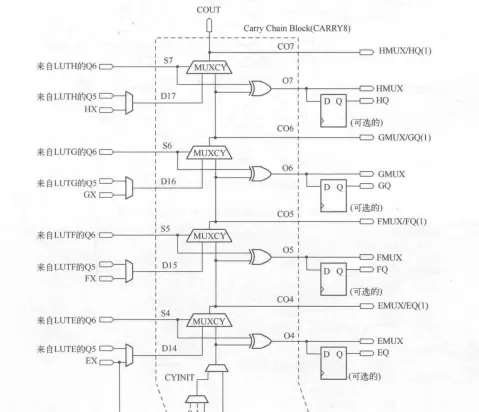

进位链

CLB内部集成了专用的快速超前进位链(Carry Chain),专用于高效执行加法与减法运算。该结构支持级联扩展,可构建多位宽算术逻辑单元。

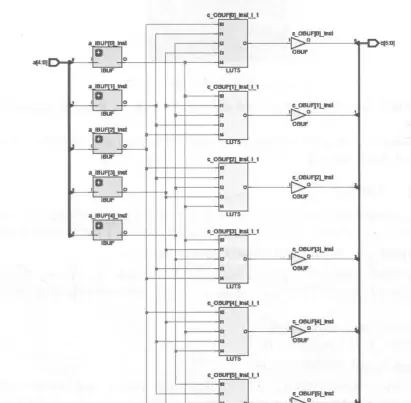

UltraScale架构中的进位链基于N-12多路复用器设计,结合查找表与进位逻辑实现高速数据选择。例如,使用xcku035-fbva676-3-e器件进行综合后,其结果如图所示,表明多路复用器通过LUT与进位逻辑共同实现。

以下是相关示例代码:

module one_bot_mux12(

input [11:0] data_in,

input [1:0] sel,

output data_out

);

wire [3:0] muxcy_sel;

wire [2:0] muxcy_cary;

LUT6 #(

.INIT(64'h0000000F003355FF)

) selection0_lut (

.J0(data_in[0]),

.J1(data_in[1]),

.J2(data_in[2]),

.J3(sel[0]),

.J4(sel[1]),

.J5(sel[2]),

.O(muxcy_sel[0])

);

endmodule

存储元素

切片中的存储资源由16个触发器或锁存器构成,支持时序逻辑设计。在SLICEM中,LUT可进一步配置为分布式RAM或移位寄存器,提供片上小型存储解决方案,适用于FIFO、状态机或数据缓存等场景。

在UltraScale架构中,每个CLB切片集成了16个存储单元,这些存储单元均可配置为边沿触发的D触发器或电平敏感的锁存器。这16个存储单元被划分为两个独立的组:上半部分和下半部分,每组包含8个单元。每个LUT的输出端连接两个存储单元,因此每两个存储单元构成一对,分别标记为FF和FF2。由此,上半部分形成A至D共4对存储单元,下半部分则对应E至H的4对。

该结构为每个CLB提供两个时钟输入以及两个置位/复位(SR)信号输入,分别服务于上半部与下半部的存储单元。对于置位/复位操作,系统支持同步和异步两种模式,增强了设计灵活性。

每个存储单元的数据输入可来源于以下多个路径:

- LUT的O6输出

- LUT的O5输出

- 直接旁路LUT的CLB输入信号(BYP模式),其中CLBX用于Q1,CLBI用于Q2

- 进位链中逻辑异或运算的结果

- 进位级联输出(CO)

- 来自多路复用器(FMUX)的一个输出(此选项对底部的LUTA不可用)

针对存储单元的初始化功能,支持以下四种方式:

- SRLOW:当SR信号有效时,执行同步或异步复位操作

- SRHIGH:当SR信号有效时,执行同步或异步置位操作

- INIT0:设备上电期间自动进行异步复位

- INIT1:设备上电期间自动进行异步置位

上述机制涵盖了存储单元作为触发器或锁存器使用时的同步与异步控制行为,具体实现方式如代码示例所示。

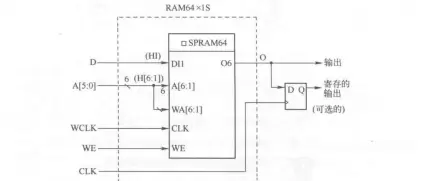

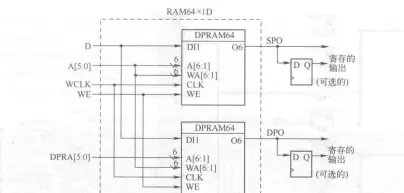

分布式RAM功能

SLICEM中的函数发生器(即LUT)能够被配置为同步RAM资源,也被称为分布式RAM。多个LUT可在SLICEM内组合使用,构建最大容量达512比特的存储结构。根据访问方式的不同,可配置为以下五种工作模式:

- 单端口模式:支持32×(1~16)位、64×(1~8)位、128×(1~4)位、256×(1~2)位及512×1位的存储配置。图示展示了64×1位单端口分布式RAM的内部结构。

- 双端口模式:支持32×(1~4)位、64×(1~4)位、128×1位和256×1位的配置。图1.15显示了64×1位双端口分布式RAM的结构布局。

- 简单双端口模式:支持32×(1~14)位和64×(1~7)位的配置。

- 四端口模式:包括32×(1~4)位、64×(1~2)位和128×1位三种规格。

- 八端口模式:仅支持64×1位的配置。

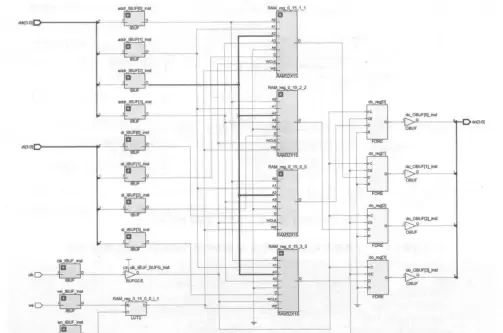

以下是一个宽度为4位、深度为16的分布式存储器的Verilog HDL代码描述示例:

该代码经综合工具处理后的实际网表示意图如下:

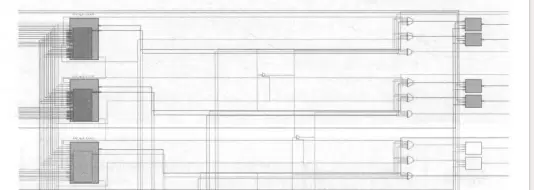

最终布线实现结果如下图所示:

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号