随着芯片制程持续向更小节点推进,5纳米、3纳米等先进工艺已逐渐成为主流。现代芯片内部集成的晶体管数量可达上百亿个,其结构之微小、运行环境之复杂,使得任何细微缺陷都可能引发整体功能失效。在此背景下,动态电压应力测试(DVS)作为保障芯片长期可靠性的核心技术手段,发挥着不可替代的作用。

一.深入理解DVS测试:原理与关键价值

DVS,即动态电压应力测试,是一种在芯片处于实际运行状态时施加变化电压进行压力验证的方法。相比传统静态测试方式,DVS能更真实地复现芯片工作过程中的电气波动,从而有效识别出仅在动态条件下才会显现的潜在故障。

1. 静态测试的技术瓶颈

- 采用恒定高电压施加(如Burn-in),缺乏动态响应模拟

- 无法还原真实场景下的电压跳变和开关瞬态效应

- 对先进制程中常见的动态退化机制(如电迁移、热载流子注入)检测能力有限

2. DVS的核心优势

- 贴近真实工况:电压在Vmin与Vmax之间周期性切换,模拟实际运行中的负载变化

- 精准捕捉动态失效:可发现HCI(热载流子注入)、EM(电迁移)等隐藏型缺陷

- 显著提升效率:将原本需24小时的老化测试压缩至4小时内完成

3. DVS与EVS对比分析

| 测试特性 | 动态电压应力测试(DVS) | 静态电压测试(EVS) |

|---|---|---|

| 电压形式 | 动态变化(方波、三角波等) | 固定直流电压 |

| 测试模式 | 模拟实际开关操作 | 施加恒定高电压 |

| 失效覆盖范围 | 动态失效机制(HCI、EM等) | 静态失效(TDDB等) |

| 测试耗时 | 几小时 | 几十小时 |

| 适用工艺节点 | 先进工艺(5nm及以下) | 成熟工艺 |

二.DVS实施流程详解

1. 测试参数设定

电压范围选择:

- 通常设置为核心工作电压的1.4至1.7倍,具体依据工艺调整

- 例如,在5nm工艺下推荐值为:逻辑电路1.6V,SRAM模块1.4V

波形类型配置:

- 方波:最常用,实现Vmin与Vmax间的快速切换

- 三角波:用于需要平滑过渡的应用场景

- 正弦波:特定用途,适用于低噪声敏感测试

关键参数配置示意图如下:

示例参数设置

dvs_params = {

'voltage_range': [0.8*Vnom, 1.5*Vnom], # 电压范围

'frequency': 1000, # 频率1kHz

'duty_cycle': 50, # 占空比50%

'temperature': 125, # 温度125°C

'duration': 4 # 持续时间4小时

}2. 完整测试执行步骤

前期准备工作:

- 与晶圆制造厂确认工艺参数及最大耐压极限

- 获取芯片设计文档与标准测试激励pattern

- 通过Shmoo图分析确定最优应力条件区间

正式测试流程:

- 逐步上电:防止因瞬间过压造成器件损伤

- 施加动态应力:结合功能性测试pattern同步运行

- 实时监控:持续采集电流、频率等关键性能指标

- 数据分析:比对应力前后各项参数的变化趋势

验收判定标准:

- 连续三次重复测试中,失效率增长不超过1%

- 对失效样本进行物理分析,定位缺陷类型与空间位置

三.技术创新突破:基于传感电路的DVS架构设计

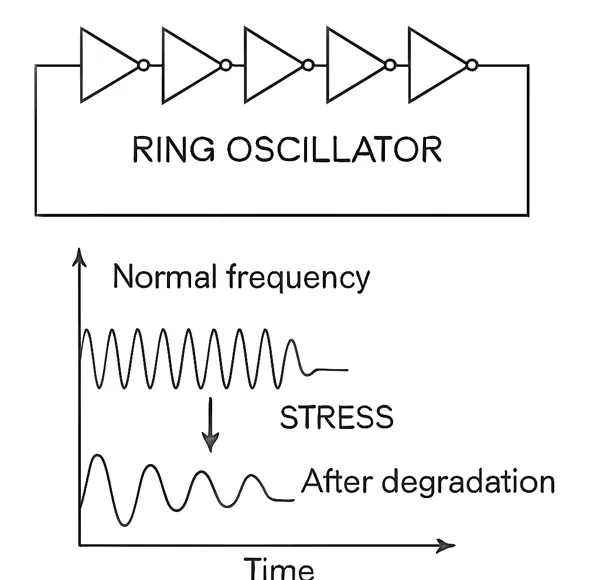

一项前沿研究揭示了传统可靠性测试的根本局限,并提出了一种革命性解决方案。其核心思想可概括为:将难以量化的模拟域性能衰退现象,转化为高度精确且易于测量的数字频率偏移信号。

这类似于将“评估运动员体能”的标准,从主观的“疲劳感”转变为客观的“心率数值变化”。

该理念依托于一种精巧的环形振荡器传感结构来实现:

- 部署“内置听诊器”:在芯片关键模块中嵌入微型环形振荡器——如同为电路安装高速心跳监测装置

- 施加电压应力:在动态运行状态下加载高于正常水平的电压

- 监测频率响应:若存在薄弱点,晶体管开关速度下降,直接反映为振荡器输出频率降低

- 数字化判别:利用计数器测量频率并与基准“黄金频率”比对,超出阈值即标记为早期失效

这一设计的重大意义在于:它成功将原本复杂的模拟可靠性评估,转化为了适合量产环境的大规模数字测试任务。不仅实现了电路层面的创新,更代表了测试理念的一次跃迁,为5nm及以下工艺节点提供了高效可靠的缺陷筛选路径。

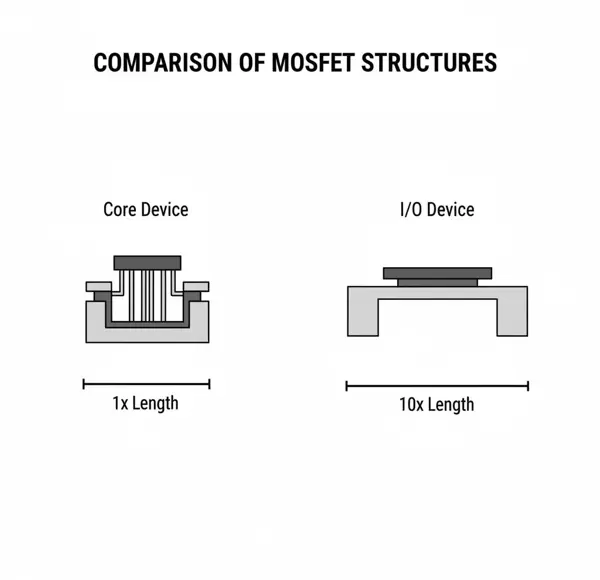

四.Core与IO的差异化测试策略解析

在DVS实践中,工程师采取了一种看似矛盾实则科学的策略:对精密的内核(Core)施加高达1.7倍的严苛电压,而对接口(IO)单元却仅使用1.2倍的温和应力。这种差异源于两类电路在物理结构与设计目标上的根本区别。

1. 内核(Core)器件的“极限耐力测试”哲学

Core是芯片的运算中枢,具有以下特征:

- 栅氧层极薄:厚度仅为5–10?,相当于数个原子层

- 工作电压低:一般为0.8–1.0V,追求极致能效

- 主要失效模式:材料级老化问题(如TDDB)

DVS策略解读:

对Core施加1.4–1.7倍电压,本质上是对马拉松选手进行极限耐力考核。通过增强电场强度(例如1.6V应力相对于1.0V工作电压提升了60%的电场),加速电子隧穿效应,提前暴露栅氧层中的微观缺陷。

2. 接口(IO)器件的“系统级抗扰测试”逻辑

IO承担外部通信职责,其设计原则完全不同:

- 厚栅氧层:达30–50?,具备更强的物理鲁棒性

- 高工作电压:支持3.3V或5V,应对复杂外部干扰

- 主要风险来源:寄生效应与系统级耦合噪声

DVS测试的关键在于平衡:既要充分激发潜在缺陷,又要避免因过度应力引发非典型失效。因此采用较低倍数(1.2倍)的电压更为稳妥,确保测试结果反映的是真实应用场景下的可靠性表现。

在摩尔定律不断推动工艺微缩的今天,DVS测试已从一种可选的技术手段演变为芯片质量控制中不可或缺的关键环节。它不仅能够高效识别早期失效风险,还能为产品长期运行的稳定性提供科学依据。随着技术进步,DVS测试将持续升级,成为半导体行业可靠性验证的新标准。

这种测试方式可类比于对防弹衣实施“临界点考验”。施加1.2倍的电压虽然表面看较为保守,但实际上已接近IO电路设计的安全极限。过高的电压并不会直接击穿电路结构,而是可能引发内部保护机制的误响应,从而导致功能异常或潜在损伤。

主要风险因素解析

- 热载流子注入(HCI):在高电压作用下,载流子获得过高能量,撞击晶体晶格,造成器件性能退化,尤其在先进制程中更为显著。

- 闩锁效应(Latch-up):轻微的电压抬升即可激活寄生的硅控整流器(SCR),形成低阻通路,引发大电流并可能导致永久性损坏。

- ESD保护电路误触发:原本用于抵御静电放电的保护二极管,在持续过压条件下可能发生非预期导通,干扰正常工作甚至引发连锁反应。

典型应用实例与成果展示

案例一:5nm手机CPU寿命预测

挑战:热载流子注入效应在常规使用环境下需多年才能显现性能衰退。

解决方案:采用DVS加速应力测试,结合物理模型外推实际使用寿命。

成果:成功预估设备在三年内的性能衰减趋势,精度达到工程可用水平。

案例二:汽车级MCU早期失效筛选

传统方法:在125°C下进行24小时静态老化处理。

DVS方案:同样温度下执行4小时动态应力测试。

成效:筛选时间缩短83%,缺陷检出率提升至99.3%,大幅提高生产效率和产品质量。

未来发展方向展望

- AI驱动参数优化:利用机器学习算法实时调整应力条件,实现个性化、高效率的测试流程。

- 3D集成协同测试:面向chiplet架构发展多芯粒联动的应力施加策略,确保系统级可靠性。

- 预测性维护模型:基于历史测试数据构建可靠性衰退预测体系,支持产品全生命周期管理。

- 标准化建设推进:推动建立统一的DVS测试规范与行业标准,促进技术普及与互认。

对于芯片设计企业及制造厂商而言,提前构建DVS测试能力,意味着在未来的市场竞争中占据先机。在这个以质量为核心竞争力的时代,DVS测试正是保障芯片可靠性的核心技术支柱之一。

雷达卡

雷达卡

京公网安备 11010802022788号

京公网安备 11010802022788号